類組:電機類 科目:固態電子元件(300G)

共3頁 第1頁

計算題(計算題應詳列計算過程,無計算過程者不予計分)

- 1. Suppose that a beam of monochromatic light with optical power P illuminates the surface of a silicon wafer, the light beam spot size is smaller than the wafer area, and some the electrons in the silicon wafer are excited from valence band to conduction band by the light. Now, if the incident optical power is doubled from P to 2P, how do the following items change, respectively? (a) The frequency of the light; (b) The energy gained by each excited electron; (c) The number of excited electrons per unit time; (d) The number of created holes per unit time; (e) The power of reflected light. (10%)

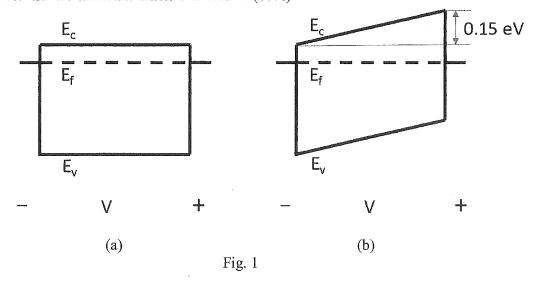

- 2. The equilibrium electronic energy band diagram (E-x diagram) of a uniformly doped silicon (Fig. 1(a)) and that of a non-uniformly doped silicon (Fig. 1(b)) are shown in Fig. 1. Please draw the E-x diagrams for the two materials when V is 0.15 V. (10%)

- 3. A semiconductor has an intrinsic carrier concentration of  $1x10^{10}$  cm<sup>-3</sup> at room temperature. (a) If the semiconductor is uniformly doped with  $1x10^{15}$  cm<sup>-3</sup> donors, what are the hole concentration and electron concentration in the material at the same temperature? (5%) (b) If the material in (a) is subsequently doped with  $1x10^{15}$  cm<sup>-3</sup> acceptors, what are the hole concentration and electron concentration in the material at the same temperature? (5%)

- 4. Consider a pn diode with a uniform doping concentration on both sides of the junction. The bandgap of the semiconductor is 0.8 eV. The doping concentration in the n-type region is  $1x10^{17}$  cm<sup>-3</sup>, where  $E_f$  is 0.2 eV below  $E_C$ . The doping concentration in the p-type region is  $5x10^{17}$  cm<sup>-3</sup>, where  $E_f$  is 0.15 eV above  $E_V$ . The depletion width in the n-type and the p-type regions is denoted as  $x_n$  and  $x_p$ , respectively

- (a) Find the ratio of  $x_n/x_p$  when this diode is in equilibrium. (5%)

- (b) Find the ratio of  $x_n/x_p$  when this diode is reverse biased at 5 V. (5%)

- (c) Find V<sub>bi</sub>. (5%)

- 5. M-S junction **A** is formed by depositing a metal with a work function of 4.6 eV ion an n-type Si with a uniform doping concentration of  $1 \times 10^{17}$  cm<sup>-3</sup>. M-S junction **B** is formed by depositing the same metal on another n-type Si with a uniform doping concentration of  $1 \times 10^{18}$  cm<sup>-3</sup>. Suppose that Si has an electron affinity of 4 eV.

- (a) Draw the band diagram of M-S junctions **A** and **B** in equilibrium on the same graph. Show  $E_f$ ,  $E_C$ ,  $E_V$  and indicate  $\phi_{bn}$ . (5%)

- (b) Plot  $1/C^2$  versus reverse bias  $V_R$  for these two M-S junctions on the same graph. Show  $V_R$  intercepts. (5%)

注意:背面有試題

類組:電機類 科目:固態電子元件(300G)

共3頁 第2頁

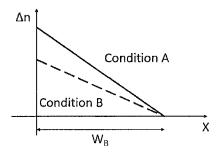

- 6. Fig. 2 shows the distribution of excess minority carrier  $\Delta n$  in the base region of a Si npn BJT operated in two conditions in forward active mode.

- (a) Which condition gives a larger collector current? Please explain. (5%).

- (b) Which condition has a larger V<sub>BE</sub>? Please explain (5%).

No points will be given if no explanation is provided.

Fig. 2

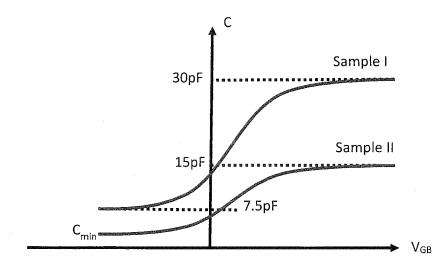

- 7. The two CV curves in Fig. 3 are measured on two MOS capacitors of the same area and on the same uniformly doped Si substrate, where  $V_{GB}$  is the voltage between gate to substrate. Sample I's gate oxide thickness is  $T_{ox1}$  and  $T_{ox2}$  for Sample II. The dielectric constants of SiO<sub>2</sub> and Si are 3.9 and 11.7, respectively. (20%)

- (a) The measurements are made under high or low frequency? (4%)

- (b) The Si substrate is n-type or p-type? (4%)

- (c) If  $T_{ox1}$ =6nm, what is  $T_{ox2}$  (nm)? (4%)

- (d) For Sample II, what is the expected  $C_{min}$ ? (4%)

- (e) At C=C<sub>min</sub>, what is the depletion width into the Si substrate? (4%)

Fig. 3

注意:背面有試題

## 台灣聯合大學系統 112 學年度碩士班招生考試試題

類組: 電機類 科目: 固態電子元件(300G)

共3頁 第3頁

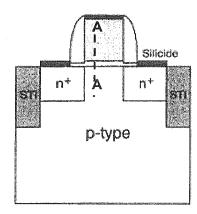

- 8. Consider a n-MOSFET of W/L=10, with its cross-section shown in Fig. 4. (15%)

- (a) Let the capacitance ratio of gate oxide and substrate be 3:2, what is its subthreshold swing (mV/decade) at 25°C? (3%)

- (b) Let the threshold voltage of this transistor be 0.4V, determined by a constant current of 1nA/(W/L), what is its off-state leakage current (i.e., drain current at zero gate voltage)? (3%)

- (c) If the work-function of the metal increases by 0.2eV, what is the new threshold voltage level? (3%)

- (d) Draw the band diagram (label Ec, Ev, Ei, Ef) along A-A' at thermal equilibrium, zero bias. (3%)

- (e) In a short channel device, when T<sub>ox</sub> increase, the drain-induced barrier lowering (DIBL) effect becomes more or less significant, why? (3%)

Fig. 4