節

所 别 資訊科學系 考 战 時間

星期

## Computer Organization and Design

Performance You are trying to decide which system to purchase and are considering two different computers M1 and M2:

| Instruction Class | CPI for M1 | CPI for M2 |

|-------------------|------------|------------|

| A                 | 4          | 2          |

| В                 | 6          | 4          |

| C                 | 8          | 3          |

The machine M1 has a clock rate of 1 GHz and M2 has a clock rate of 500 MHz.

- (a) [3 points] Compare the two processors' peak performance in terms of MIPS.

- (b) [3 points] Consider the three compilers C1, C2, and C3 that produce the frequency results shown below:

| Instruction Class | C1  | C2  | C3  |

|-------------------|-----|-----|-----|

| Α                 | 30% | 30% | 50% |

| В                 | 50% | 20% | 30% |

| С                 | 20% | 50% | 20% |

For compiler C1, compare M1 and M2. Which processor is faster and by how much? (c) [4 points] Assuming that any of the three compilers can be used on M1 or M2, which of these two machines and which compiler should be purchased?

- what does it represent, assuming that it is

- a. a two's complement integer?

- b. an unsigned integer?

- c. a single precision floating-point number?

- cf: You are not required to calculate the final results for parts (a) and (b), simply express them in terms of the summation of 2's power, such as 2^16 + 2^10+...+ 2 +1

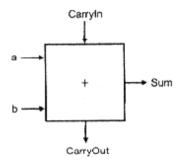

- 1-bit full adder [10 points] Express the CarryOut and Sum bits as logical equations of the inputs a, b and Carryln, then implement the Sum bit by logic gates.

交 備 馘 題 隨

考試科目計算機系统 所别資訊科學品考試時間 月 日上午第 節

## 4. Pipelining

- (a) [4 points] Explain the three types of hazards encountered in pipelining. Which one of the hazards can be handled by forwarding?

- (b) [6 points] Identify all of the data dependencies in the following code. Which dependencies are data hazards that will be resolved via forwarding?

add \$2, \$5, \$4 add \$4, \$2, \$5 sw \$5, 100(\$2) add \$3, \$2, \$4

- 5. Performance of Multilevel Caches Suppose we have a processor with a base CPI of 1.0, assuming all references hit in the primary cache, and a clock rate of 1GHz. Assume a main memory access time of 150ns, including all the miss handling. Suppose the miss rate per instruction at the primary cache is 6%.

- (a) [4 points] What is the effective CPI for this machine?

- (b) [6 points] We would like to double the performance of the CPU by adding a second level cache. Suppose the amount of the 2<sup>nd</sup> level cache is large enough to reduce the miss rate in memory to 2%, calculate the maximum allowable access time of this 2<sup>nd</sup> level cache.

**試題隨卷繳交**

備

考

考試科目(作業年記) 所列 >复記手科學采 考試時間 月 日上午第 節

There are five problems in this computer systems: operating systems examination. Please do all of them. The weights for each problem is indicated after the problem number.

6. (10%) The first known correct software solution to the critical-section problem for two processes was developed by Dekker. The two processes, P<sub>0</sub> and P<sub>1</sub>, share the following variables:

```

var flag: array[0..1]of boolean;(*initially false*)

turn:0..1;

```

The structure of process  $P_i(i = 0 \text{ or } 1)$ , with  $P_j(j = 1 \text{ or } 0)$  being the other process, is shown in the following figure:

## repeat

```

| flag[i] := true;

| while flag[j]

| do if turn = j

| then begin

| flag[i] := false;

| while turn = j do no-op;

| flag[i] := true;

| end;

```

critical section

```

turn := j;

flag[i] := false;

```

remainder section

until false;

Figure 1: The structure of process  $P_i$  in Dekker's algorithm

Prove that the algorithm satisfies all three requirements for the criticalsection problem.

備 考 試題隨卷繳交

考試科目(1年第年稅)所及

别爱视料

考試時

月 日上 午第 星期 下 午第

7. (10%)(a)Multithreading is a commonly used programming technique. Describe three different ways that threads could be implemented. (b)Explain how these ways compare to the Linux clone mechanism. When might each alternative mechanism be better or worse than using clones?

- P. (10%)(a) When do page faults occur? Describe the actions taken by the

operating system when a page fault occurs.

- (b) An operating system supports a paged virtual memory, using a central processor with a cycle time of 2 microsecond. It costs an additional 2 microsecond to access a page other than the current one. Pages have 2000 words, and the paging device is a drum that rotates at 3600 revolutions per minute, and transfers 1 million words per second. The following statistical measurements were obtained from the system:

- 2 percent of all instructions executed accessed a page other than the current page.

- Of the instructions that assessed another page, 85 percent accessed a page already in memory.

- When a new page was required, the replaced page was modified 40 percent of the time.

Calculate the effective instruction time on this system, assuming that the system is running one process only, and that the processor is idle during drum transfers.

- 9. (10%)(a)SUN NFS aims to support heterogeneous distributed systems by the provision of an operating system-independent file service. What are the key decisions that the implementer of an NFS server for an operating system other than UNIX would have to take?

(b) What constraints should an underlying filing system obey to be

- (b) What constraints should an underlying filing system obey to be suitable for the implementation of NFS servers?

- /c. (10%)(a)PGP(Pretty Good Privacy) is widely used to secure email communication. Describe the steps that a pair of users using PGP must take before they can exchange email messages with privacy and authenticity guarantees.(The PGP negotiation is an instance of the hybrid scheme.)

- (b) How would email be sent to a large list of recipients using PGP or a similar scheme? Suggest a scheme that is simpler and faster when the list is used frequently.

備 考試題隨卷繳

交