## 國立台灣科技大學一百學年度碩士班招生試題

系所組別: 電機工程系碩士班戊組

科 目: 計算機概論

(總分為100分)

1. Explain the following terminology pairs and identify the differences between them. (15%)

(a) Instruction-level parallelism / Data-level parallelism (5%)

(b) Multiprogramming OS / Multiprocessing OS (5%)

(c) Write through cache /Write back cache (5%)

2. The substantial differences between the circumstances under which a processor-memory bus and an I/O bus or backplane bus are designed lead to two different schemes for communication on the bus: synchronous and asynchronous. Please explain the two terms. (5%)

3. Consider the machine with three instruction classes, X, Y and Z, and CPI for these classes are, 1, 2, and 3, respectively. Suppose we measure the code for the same program from two different compilers and obtain the following data. Assume that the machine's clock rate is 400 MHz. Which code sequence will execute faster according to MIPS? (10%)

| Code from   | Instruction counts (in billions) for each instruction class |   |   |

|-------------|-------------------------------------------------------------|---|---|

|             | Х                                                           | Y | Z |

| Compiler I  | 5                                                           | 1 | 1 |

| Compiler II | 10                                                          | 1 | 1 |

4. A program runs in 12.5 seconds on computer A, which has a 400-MHz clock. A computer designer is trying to build a machine, C, that will run this program in 8 seconds. The designer has determined that a substantial increase in the clock rate is possible, but this increase will affect the rest of the CPU design, causing machine C to require 1.44 times as many clock cycles as machine A for this program. What clock rate should be to the target? (10%)

5. Consider the pipelined control using the instruction mix for gcc. The instruction mix for gcc is 25% loads, 12% stores, 18% branches, 3% jumps, and 42% all the rest of the mix. The operation times for the major functional units are 2 ns for memory access, 2 ns for ALU operation, and 1 ns for register file read/ write. For pipelined execution, assume that half of the load instructions are immediately followed by an instruction that uses the result, that the branch delay on misprediction is 1 clock cycle, and that one-quarter of the branches are mispredicted. Assume that jumps always pay 1 full clock cycle of delay, so their average time is 2 clock cycles. What's the average instruction time? (10%)

6. Use C or C++ programming language to implement queue operations to insert/delete an element to/from an assigned queue. (14%)

7. Design a ternary Huffman code, using 0, 1, and 2 as letters, for a source with output alphabet probabilities given by {0.05, 0.1, 0.15, 0.17, 0.18, 0.22, 0.13}. What is the resulting average code-word length? Compare the average code-word length with the entropy of the source. (In what base would you compute the logarithms in the expression for the entropy for a meaningful comparison?) (16%)

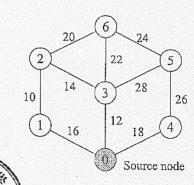

8. Please construct a minimum cost spanning tree for the undirected connected graph with the cost beside each link shown below by (20%)

(a) Kruskal's algorithm without any constrain. (10%)

(b) Kruskal's algorithm with the constrain that a branch contains at most three links. (10%)

(Note that mark the sequence number beside each link)