## 國立高雄應用科技大學 100 學年度碩士班招生考試 電子工程系(丙組)

准考證號碼□□□□□□□ (考生必須填寫)

## 計算機結構

試題 共3頁,第1頁

注意:a. 本試題共8題,共100分。

- b. 作答時不必抄題。

- c. 考生作答前請詳閱答案卷之考生注意事項。

- 1. Refer to the following code segment in MIPS instruction set architecture. (10%)

- (a) Explain the operation performed by each instruction.

- (b) What value is in register t0 after the execution of this code segment?

addi \$t0,\$zero,0

addi \$t1,\$zero,0

addi \$t2,\$zero,10

LOOP: addi \$t1,\$t1,1

add \$t0,\$t0,\$t1 bne \$t1,\$t2,LOOP

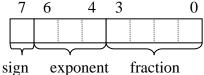

2. Consider the following fictional floating-point number representation inspired by IEEE 754 with an exponent bias of 3. (15%)

- sign exponent maction

- (a) Represent  $5_{10}$  using the representation.

- (b) Represent  $0.1875_{10}$  using the representation.

- (c) Represent  $5_{10} + 0.1875_{10}$  using the representation.

- 3. Assume that multiply instructions take 12 cycles and account for 20% of the instructions in a typical program, and the other 80% of the instructions require an average of 4 cycles for each instruction. A proposal of performance improvement can reduce the number of cycles required for multiplication to 8 cycles, but requires a 20% increase in the cycle time. Is this proposal profitable in execution time? Please justify your answer (10%)

- 4. For a multi-cycle CPU, the frequency of occurrence and number of required cycles of 5 classes of instructions are tabulated as follows. Please evaluate the weighted average CPI (Cycle per Instruction). (10%)

| Instruction Class   | Frequency of Occurrence | Number of Required Cycles |  |

|---------------------|-------------------------|---------------------------|--|

| Load                | 25%                     | 5                         |  |

| Store               | 10%                     | 5                         |  |

| ALU Instruction 50% |                         | 3                         |  |

| Conditional Branch  | 10%                     | 4                         |  |

| Jump                | 5%                      | 4                         |  |

- 5. The 5 stages and the time they take in the execution of an instruction are listed below. Please evaluate the time it take to execute 10 instructions for (10%)

- (a) A single-cycle machine.

- (b) A pipeline machine.

| IF    | ID    | EX    | MEM   | WB    |

|-------|-------|-------|-------|-------|

| 15 ns | 10 ns | 10 ns | 20 ns | 10 ns |

- 6. List and explain those "hazards" in applying pipelining technique to CPU design for improved performance in instruction execution. (10%)

- 7. For a typical memory system, (15%)

- (a) Draw the entire memory hierarchy, from registers in CPU down to auxiliary storage, indicating the trend of access speed, size and unit cost.

- (b) Explain the similarity and difference between the concepts of cache memory and virtual memory.

## 試題 共3頁,第3頁

- 8. Explain the following terminologies. (20%)

- (a) Microcode

- (b) CISC vs. RISC

- (c) Translation-Lookaside Buffer

- (d) Direct Memory Access

- (e) SIMD (in the context of multiprocessor)