科目: 邏輯設計

題號: 429

共 429

1. (10%) Given two unknown 4-bit numbers  $N_1$  and  $N_2$ , their addition in two's complement yields no overflow whereas their addition in one's complement yields overflow (with end-around carry). What are the possible  $(N_1, N_2)$  pairs?

- 2. (10%) Consider a Boolean function f(a,b,c,d) with f(0,b,c,d) = c' + cd' and f(1,b,c,d) = bd + cd'. Express f in minimum product of sums (POS). In the two-level circuit implementation of the minimum POS expression, can static 1-hazards occur? How about static 0-hazards? How can you make the POS expression hazard free?

- 3. (20%) Given a Boolean function f(a,b,c,d) with the properties f(a,b,c,d) = f(b,a,c,d) and f(a,b,c,d) = f(a,c',b',d) (notice the complements), suppose f is partially known as shown in the following Karnaugh map.

| а  | b |    |    |    |     |

|----|---|----|----|----|-----|

| cd | / | 00 | 01 | 11 | 10  |

|    | 0 | 0  |    |    |     |

| 0  | 1 |    |    | 0  | 1   |

| 1  | 1 | 0  | 1  |    | 100 |

| 1  | 0 |    |    | 0  |     |

Which of the unknown minterms (m1, m2, m3, m4, m5, m6, m8, m10, m11, m12, m15) are uniquely determined? What are their values? How many functions satisfy the above constraints? Among these functions, which one has the simplest SOP expression?

科目: 邏輯設計

題號: 429

共 4 頁之第 7 頁

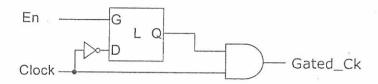

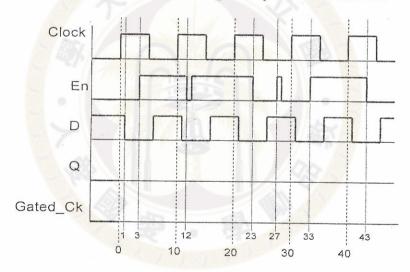

4. (15%) Consider the following circuit, which consists of a gated D-latch, an inverter, and an AND gate. Suppose all of these components have 1 unit delay.

- (a) (3%) Write down the truth table of the gated D latch.

- (b) (7%) Complete the following timing chart for signals "Q" and "Gated\_Ck" by assuming the glitches of the "En" signal has pulse width 1 time unit.

(c) (5%) Please describe the function of the above circuit. How can it be used? In what applications can this circuit be useful?

科目: 邏輯設計

題號: 429

共 4 頁之第 3 頁

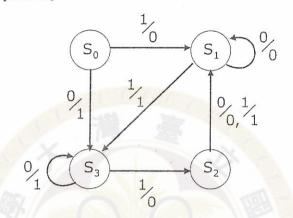

5. (15%) Assume we are given an encoder with the following state graph, where  $S_0$  is the initial state. Accordingly for any input sequence  $\sigma_I$ , the encoder produces an output sequence  $\sigma_O$ .

- (a) (10%) Design a decoder, which re-produces  $\sigma_1$  by receiving  $\sigma_0$  from the encoder.

- (b) (5%) Is your decoder state minimized? If not, perform state minimization on your decoder.

- 6. (10%) Given two finite state machines (FSMs) possibly with different numbers of states, how can you tell whether they are equivalent, i.e., having the same input-output behavior? Please justify your method.

科目: 邏輯設計

題號: 429

題號: 429 共 4 頁之第 4 頁

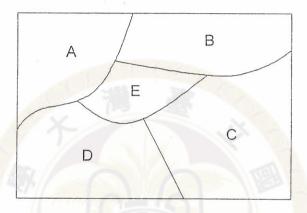

7. (20%) Given a world map with five countries A, B, C, D, and E as shown below, to color the map we require that 1) each country must receive one color, and 2) two adjacent countries must receive different colors. Moreover, we would like to use as few colors as possible to color the whole map.

Please formulate the above map coloring problem as a sum-of-products (SOP) minimization problem such that in the minimized SOP expression each product term corresponds to a distinct color used, and the literals of a product term correspond to the countries receiving the same color.

- (a) (15%) Please specify the (incompletely specified) function f(A,B,C,D,E) for SOP minimization. What are the minterms for f=1 and what are the minterms for f=0? (The rest are don't care minterms.) Please justify your answer.

- (b) (5%) What is the final expression after SOP minimization? What is the corresponding map coloring?