## 碩士班 招生試題卷 元智大學 102 學年度研究所

電機工程學系碩 系(所)別: 電子工程組

用紙第 | 頁共 乙頁

●不可使用電子計算機

- 1. (20%) Given an n-channel MOSFET with  $k'_n = 100 \mu \text{A/V}^2$ ,  $V_{tn} = 0.7$ V, and W/L = 10, find the drain current  $i_D$  in the following cases: (a)  $v_{GS} = 3 \text{ V}$  and  $v_{DS} = 1 \text{ V}$  (10%) (b)  $v_{GS} = 2 \text{ V}$  and  $v_{DS} = 1.3 \text{ V}$  (10%)

- 2. (10%) Please sketch the pull-down network (PDN) of a MOS logic circuit that realizes the function  $Y = \overline{A} + \overline{B}(\overline{C} + \overline{D})$ .

- 3. (10%) Please describe the static power dissipation and dynamic power dissipation for a complementary metal-oxide-semiconductor (CMOS) logic-circuit family.

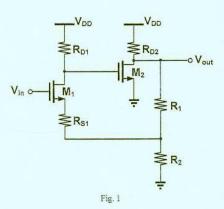

- 4. (55%)A two stage amplifier with feedback network is shown in Fig. 1. For the following circuit, assume  $\lambda = 0$  and transconductances of transistors M1 and M2 are gm1 and gm2, respectively. Meanwhile,  $R_1 + R_2 >> R_{D2}$

- (a) Please indicate which transistor will be suffered from body effect. (5%)

- (b) What components construct the first stage of the amplifier? (5%)

- (c) What components construct the second stage? (5%)

- (d) What components construct the feedback network? (5%)

- (e) What kind of feedback topology is it? (5%)

- (f) Please derive the open-loop input impedance? (5%)

- (g) Please derive the open-loop output impedance? (5%)

- (h) Please derive the open-loop voltage gain? (5%)

- (i) Please derive the closed-loop voltage gain? (5%)

- (j) Please derive the closed-loop input impedance? (5%)

- (k) Please derive the closed-loop output impedance? (5%)

## 元智大學 102 學年度研究所 碩士班 招生試題卷

条(所)別: 電機工程學系領 紅別: 電子工程組 土班

科目: 電子學

用紙第 2 頁共 2 頁

●不可使用電子計算機

(2) (5%) Please explain the Miller's Theorem.

P 161

102161