## 國立中正大學 102 學年度碩士班招生考試試題系所別:光機電整合工程研究所 科目:電子學

第2節

科目:電子學第/頁,共2頁

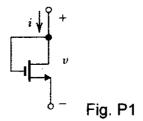

1. (10%) Fig. P1 shows an NMOS transistor with its drain and gate terminals connected together. Find the  $i-\nu$  relationship of the resulting two-terminal device in terms of the MOSFET parameters  $k_n = k_n^i(W/L)$  and  $V_m$ . Neglect channel-length modulation.

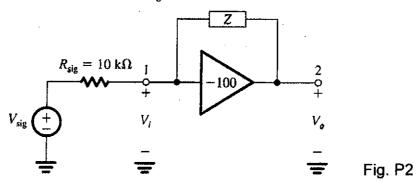

2. (20%) Fig. P2 shows an ideal voltage amplifier having a gain of -100 V/V with an impedance Z connected between its output and input terminals. Find the Miller equivalent circuit when Z is (a) a 1-M $\Omega$  resistance (b) a 1-pF capacitance. In each case, use the equivalent circuit to determine  $V_o/V_{sig}$ .

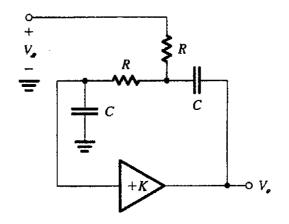

3. (20%) Fig. P3 shows a positive-feedback circuit. (a) Find the loop transmission L(s) and the characteristic equation. (b) Sketch a root-locus diagram for varying K, and find the value of K that makes the circuit oscillate.

Fig. P3

第2節

第2頁,共2頁

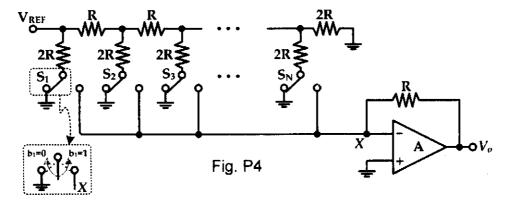

- 4. The operational amplifier (OPA) shown in Fig. P4 is an ideal OPA, and the switches  $S_{i|i=1\sim N}$  are controlled by the controlling signals  $b_{i|i=1\sim N}$ , respectively.

- (a) Please derive the output  $V_0$  using known parameters  $V_{REF}$ , R, and  $b_{||i=1\sim N}$ . (10%)

- (b) In the case of  $V_{REF}$  = 2 V, what the minimum bit number (N) of b<sub>i</sub> is required to generate an output ( $V_o$ ) of -1.8125 V and what is the corresponding  $b_{i|i=1-N}$ . (5%)

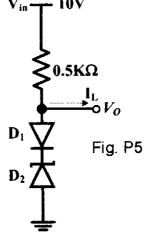

- 5. Consider the voltage regulation circuit shown in Fig. P5 for the case of V<sub>in</sub> = 10 V. Assume the diode D<sub>1</sub> to have a 0.7-V drop at 5 mA current while D<sub>2</sub> is a 6.8-V zener diode with a 6.8-V drop at 5 mA current, and an incremental resistance of 20 Ω. (Note: thermal voltage V<sub>in</sub> = 25 mV)

- (a) Determine the line regulation ( $\Delta V_{O}/\Delta V_{in}$ ). (6%)

- (b) Determine the load regulation ( $\Delta V_0/\Delta I_1$ ). (6%)

- 6. (a) Please sketch the input/output characteristic of a logic inverter, also explain the concepts of noise margin using the input/output characteristic. (5%)

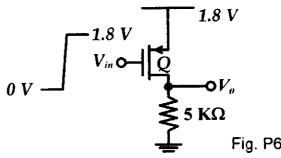

- (b) Fig. P6 shows an inverter circuit, please find the output high level ( $V_{OH}$ ) and output low level ( $V_{OL}$ ). Assume that PMOS transistor Q has the (W/L) ratio of 100,  $\mu_p C_{OX} = 50 \ \mu A/V^2$ ,  $\lambda_p = 0 \ V^{-1}$ , and  $|V_{tp}| = 0.8 \ V$ . (10%)

7. Design a row decoder for an 8 words  $\times$  8-bit SRAM, please show the circuit in transistor level. (8%)