## 國立成功大學 112學年度碩士班招生考試試題

編 號: 41

系 所: 光電科學與工程學系

科 目:電子學

日期:0207

節 次:第1節

備 註:不可使用計算機

國立成功大學 112 學年度碩士班招生考試試題

編號: 41

系

所:光電科學與工程學系

考試科目:電子學

考試日期:0207,節次:1

## 第1頁,共4頁

※ 考生請注意:本試題不可使用計算機。 請於答案卷(卡)作答,於本試題紙上作答者,不予計分。

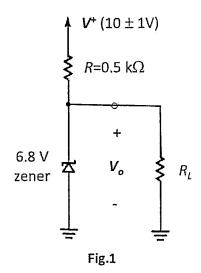

- 1. The zener diode in the circuit of Fig.1 is specified to have  $V_z$ =6.8V at  $I_z$ =5 mA,  $r_z$ =20  $\Omega$  and  $I_{zk}$ =0.2 mA. The power supply voltage V\*=10V. Please find the right items.

- (A)  $V_o = 6.83$  V with no load (B)  $I_L=13.6$  mA when  $R_L=0.5$  K $\Omega$  (C)  $V_o = 5$  V when  $R_L=0.5$  K $\Omega$  (D)  $I_Z=6.35$  mA with no load (6%)

- 2. The threshold voltage will increase for an n-channel MOS FET when (A)increase the reverse bias of substrate (B) decrease the doping concentration of substrate (C)increase the thickness of gate oxide (D) increase the gate length. (3%)

- 3. Which of the following statement(s) is(are) true(A)The BJT transconductance increases exponentially with respect to V<sub>BE</sub>.(B)The MOS FET's transconductance increases linearly with respect to V<sub>GS</sub>.(C)A PMOS FET has four terminals(D)Compared with MOS FET, BJT device has higher input impedance. (3%)

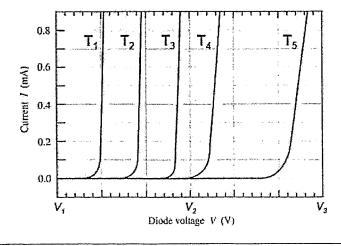

- 4. As shown in Fig. 2, if the five forward I-V curves correspond to a GaAs junction diode operated at different temperatures, please identify which of the following item(s) is(are) true.(A) $T_1>T_2(B)T_3>T_4(C)T_2>T_5(D)T_3>T_2(E)T_5>T_4(3\%)$

Fig. 2

## 國立成功大學 112 學年度碩士班招生考試試題

系 所:光電科學與工程學系

考試科目:電子學

考試日期:0207,節次:1

第2頁,共4頁

編號: 41

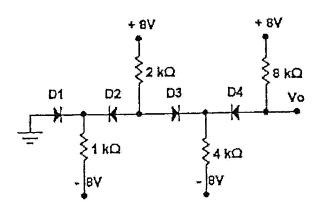

5. As shown in Fig.3, the currents  $I_{D1}$ ,  $I_{D2}$ ,  $I_{D3}$ ,  $I_{D4}$ , in each of the diodes  $D_1$ ,  $D_2$ ,  $D_3$ ,  $D_4$ . When diodes are assumed to be ideal, which of the following item(s) is(are) true (A)  $I_{D1}$ = 5mA,  $I_{D2}$ =2mA (B)  $I_{D3}$ =1 mA,  $I_{D4}$ =1 mA (C)  $V_0$ =1 V,  $I_{D2}$ =3 mA (D)  $I_{D3}$ =1 mA,  $V_0$ =0 V (10%)

Fig.3

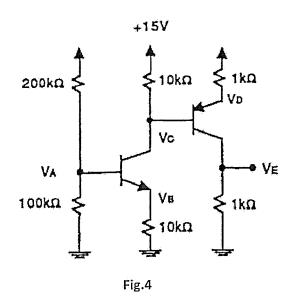

6. If the  $\beta$  is equal to 100 for transistors in Fig.4, which of the following item(s) is(are) true (A) $V_A$ =4.73 V,  $V_E$ =1.90 V (B)  $V_C$ =11.31 V,  $V_B$ =4.03 V (C)  $V_E$ =2.90 V,  $V_D$ =12.07 V (D)  $V_B$ =3.03 V,  $V_D$ =12.07 V (10%)

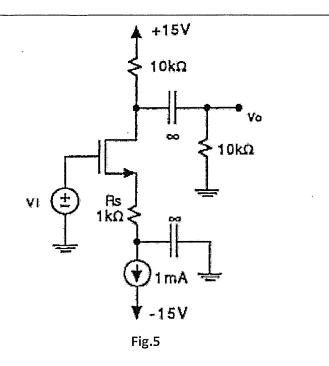

7. As shown in Fig.5,  $g_m=1$  mA/V and  $r_0=100$  k $\Omega$ . Note that while the lower end of  $r_0$  is not actually grounded, the signal there is small. Assume it to be zero. (A)Find  $V_0/V_i=?$  (B)If  $R_s=0$ ,  $V_0/V_i=?$  (C) If  $R_s=3.76$  k $\Omega$ ,  $V_0/V_i=?$  (15%)

國立成功大學 112 學年度碩士班招生考試試題

系 所:光電科學與工程學系

考試科目:電子學

考試日期:0207,節次:1

第3頁,共4頁

編號: 41

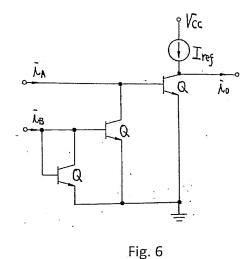

8. All BJT transistors in circuit shown in Fig. 6 are identical and have current gain ( $\beta$ ) >> 1. Please find i<sub>0</sub> in terms of i<sub>A</sub> and i<sub>B</sub>. (10%)

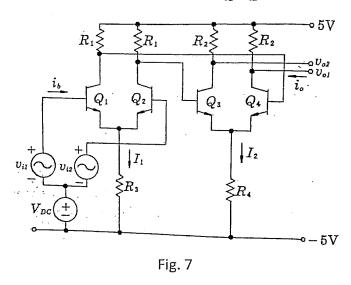

- 9. A two-stage differential amplifier is shown in Fig. 7. All transistors in circuit are identical and have infinity Early voltage,  $V_{BE(on)}$  of 0.7 V, and current gain ( $\beta$ ) of 50.  $V_{DC}$  in circuit is 5 V. (30%)

- (a) Determine values of  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$  that could meet  $R_{id} = 1$  k $\Omega$  ( $R_{id}$  is the differential-mode input resistance, defined as the ratio of differential input voltage ( $v_{id} = v_{i1} v_{i2}$ ) to the input current  $i_b$ ),  $R_{od} = 150 \Omega$  ( $R_{od}$  is the differential-mode output resistance, defined as the ratio of differential input voltage ( $v_{od} = v_{o1} v_{o2}$ ) to the input current  $i_o$ ),  $I_1R_1 = 3$   $V_{BE(on)}$ , and  $I_2R_2 = 2V_{BE(on)}$ .

- (b) Find the differential-mode voltage gain  $A_d = \frac{v_{o1} v_{o2}}{v_{i1} v_{i2}}$ .

編號: 41

## 國立成功大學 112 學年度碩士班招生考試試題

系 所:光電科學與工程學系

考試科目:電子學

考試日期:0207,節次:1

第4頁,共4頁

(c) Find the Find the differential-mode voltage gain  $A_c = \frac{v_{o1} + v_{o2}}{v_{i1} + v_{i2}}$ .

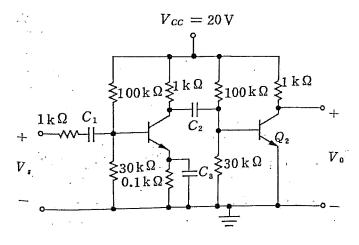

- 10. Figure 8 shows a multiple stage amplifier.  $Q_1$  in circuit has  $\beta$  = 100 and  $r_{\pi}$  = 1 k $\Omega$ .  $Q_2$  in circuit has  $\beta$  = 100 and  $r_{\pi}$  = 0.5 k $\Omega$ . (10%)

- (a) Determine the capacitors  $C_1$ ,  $C_2$ , and  $C_3$  in Fig. 8 which the lower 3dB frequency of circuit is 100 Hz.

- (b) Find the overall voltage gain of the circuit in Fig. 8.

Fig. 8