系所:電子系

本試題共 5 題,每題得分如各題中所示,共計 100 分,請依題號作答並將答案寫在答案卷 上,違者不予計分。

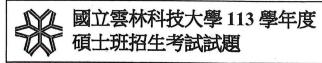

1.(10 分) Suppose in Fig. P1, the diodes carry a current of 4 mA and the load, a current of 18 mA. If the load current increases to 19 mA, what is the change in the total voltage across the three diodes? Assume  $R_1$  is much greater than  $3r_d$  and the thermal voltage ( $V_T$ ) is 26 mV.

Fig. P1

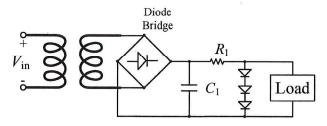

- 2. Compute the input resistance of the circuits depicted in Fig. P2. Assume  $V_A = \infty$ .

- (a) (5 分) find the input resistance of  $R_{in1}$

- (b) (10 分) find the input resistance of  $R_{in2}$

- (c) (10 分) find the input resistance of  $R_{in3}$

Fig. P2

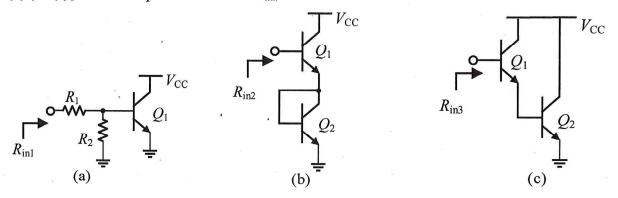

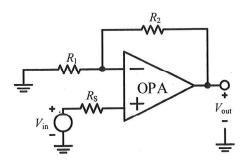

3. (15 分)The integrator of Fig. P3 must operate with frequencies as low as 1.2 kHz while providing an output offset of less than 19 mV with an OPA offset of 3 mV. Determine the required values of  $R_1$  and  $R_2$  if  $C_1 \leq 120$  pF.

Fig. P3

## 國立雲林科技大學 113 學年度 碩士班招生考試試顯

系所:電子系

科目:電子學

- 4. Fig. P4 shows a negative feedback loop circuit.

- (a)  $(10 \, \text{f})$  Find the loop gain  $A\beta$  for which the sensitivity of closed-loop gain to open loop gain  $(1+A\beta)^{-1}$  is -20 dB.

- (b) (10 %) What is the  $A\beta$  value when the sensitivity becomes 1/2?

Fig. P4

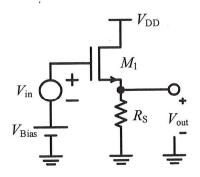

- 5. As shown in the circuit diagram in Fig. P5, if its voltage gain is 0.8, the transistor channel's width-to-length ratio is 200 (W/L =200). Its transistor parameters are:  $\mu_n C_{ox} = 200 \,\mu\text{A/V}^2$ ,  $R_S = 0.5 \,\text{k}\Omega$ , and  $V_{TH} = 0.4 \,\text{V}$ ,  $\lambda = 0$ , then:

- (a) (10 分) What is the name of this circuit?

- (b) (10 %) What should the transconductance  $g_m$  from the MOS small signal model be?

- (c) (5 分) What should the  $I_D$  current be in this case?

- (d) (5  $\Re$ ) What should be the appropriate  $V_{\text{Bias}}$ ?

Fig. P5