## 國立臺灣師範大學 109 學年度碩士班招生考試試題

科目:計算機系統 適用系所:資訊工程學系

注意:1.本試題共 3 頁,請依序在答案卷上作答,並標明題號,不必抄題。2.答案必須寫在指定作答區內,否則依規定扣分。

1. (10 points) Convert the following 16-bit hexadecimal numbers to binary numbers.

- (a) (5 points)  $7B22_{hex}$

- (b) (5 points) F12E<sub>hex</sub>

- 2. (15 points) Consider a RISC processor with separate instruction and data memories. Suppose the following code sequence is executed on the processor.

```

LW

R4,16(R8);

R4 \leftarrow MEM[R8+16]

LW

R5,20(R8);

R5 \leftarrow MEM[R8+20]

SUB

R3,R4,R5;

R3 \leftarrow R4-R5

ADD

R9,R7,R3;

R9 ← R7+R3

LW

R10,24(R8);

R10 \leftarrow MEM[R8+24]

ADD

R1,R10,R9;

R1 ← R10+R9

SW

R9,28(R8);

MEM[R8+28] \leftarrow R9

SW

MEM[R8+32] \leftarrow R1

R1,32(R8);

```

Assume that the execution of the code sequence takes 20 clock cycles. The clock cycle time of the processor is 5 ns.

- (a) (3 points) Find the Clock cycles Per Instruction (CPI) of the code sequence.

- (b) (3 points) Compute the CPU time (in ns) of the code sequence.

- (c) (3 points) Determine the number of accesses to the instruction memory.

- (d) (3 points) Determine the number of accesses to the data memory.

- (e) (3 points) Identify all the instructions where data memory accesses are NOT required.

- 3. (10 points) Consider a RISC processor with 5-stage (i.e., IF, ID, EX, MEM, WB) pipeline. Suppose the pipeline contains data forwarding and hazard detection units. Furthermore, separate instruction and data memories are used so that structural hazards for memory accesses can be avoided.

Suppose there are no cache misses and structural hazards. Find the number of clock cycles required for the execution of the following code sequences.

(a)

ADD R3,R4,R5; R3 ← R4+R5

ADD R6,R9,R3; R6 ← R9+R3

ADD R1,R2, R6 R1← R2+R6

## 國立臺灣師範大學 109 學年度碩士班招生考試試題

(b)

LW R3,16(R10); R3  $\leftarrow$  MEM[R10+16] ADD R6,R9,R3; R6  $\leftarrow$  R9+R3 SUB R12,R6,R7; R12  $\leftarrow$  R6-R7

- 4. (15 points) Consider a direct mapped cache with 32 cache blocks. The miss rate for accessing the cache is 0.25 misses per memory access. Assume hit time of the cache is 1 clock cycle, and miss penalty is 200 clock cycles.

- (a) (5 分) What cache block number of the cache does block address 321 mapped to?

- (b) (5 points) What is the Average Memory Access Time (AMAT) of the cache (in clock cycles)?

- (c) (5 points) Suppose there are 500 memory accesses for the execution of a code sequence. Determine the total number of memory-stalled clock cycles for the execution of the sequence.

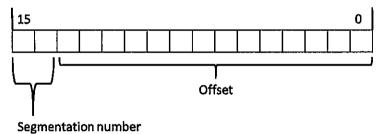

- 5. (8 points) Consider the following virtual address format and segmentation table. Determine the physical addresses for the following virtual addresses.

| Segment | Base                | Length              |

|---------|---------------------|---------------------|

| 0       | C400 hex            | 1100 hex            |

| 1       | 6200 <sub>hex</sub> | 1300 hex            |

| 2       | AA00 <sub>hex</sub> | 1250 hex            |

| 3       | 3000 <sub>hex</sub> | 1000 <sub>hex</sub> |

- (a) (4 points) 5240 hex

- (b) (4 points) B130 hex

- 6. (12 points) Consider the following processes. Determine the average waiting time of the execution for the following scheduling algorithms.

## 國立臺灣師範大學 109 學年度碩士班招生考試試題

| Process | CPU burst time | Arrival time |

|---------|----------------|--------------|

| P1      | 1              | 0            |

| P2      | 4              | 2            |

| P3      | 5              | 3            |

| P4      | 4              | 5            |

| P5      | 7              | 9            |

- (a) (6 points) Non-preemptive shortest-job-first scheduling

- (b) (6 points) Round-robin scheduling with time slice = 3 time units

- 7. (12 points) Consider the following page reference string.

Assume that we use demand paging with five frames. How many page faults would occur for the following replacement algorithms?

- (a) (6 points) First-in, first out replacement

- (b) (6 points) Least recently used replacement

- 8. (10 points) Amdahl's Law is a formula that identifies potential performance gains from adding additional computing cores to an application that has both serial and parallel components. If P is the portion of the application that can be performed parallelly on a system with N processing cores, what is the maximum speedup?

- 9. (8 points) Including the initial parent process, how many processes are created by the program shown below?

```

#include <stdio.h>

#include <unistd.h>

int main() {

int i;

for(i=0; i<8; i++)

fork();

return 0;

}</pre>

```