編號: 176, 202 國立成功大學 109 學年度碩士班招生考試試題

系 所:電機工程學系、電機資訊、趨視一微電、奈夫斯和

考試科目:電子學 考試日期:0210,節次:1

### 第1頁,共3頁

- ※ 考生請注意:本試題可使用計算機。 請於答案卷(卡)作答,於本試題紙上作答者,不予計分。

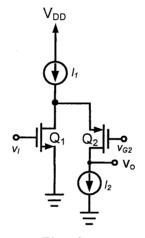

- 1. Consider the folded-cascode amplifier of Fig. 1 for the following case:  $V_{DD}$ =1.8 V,  $\mu_p C_{ox}$ =1/4 $\mu_n C_{ox}$ , and  $V_{tn}$ =-  $V_{tp}$ =0.5 V, To operate  $Q_1$  and  $Q_2$  at equal bias currents I,  $I_1$ =2I and  $I_2$ =I. While current source  $I_1$  is implemented using the simple circuit and current source  $I_2$  is realized using a cascoded circuit. The transistor W/L ratios are selected so that each operates at an overdrive voltage of 0.2 V. (20%)

- (a) What must the relationship of  $(W/L)_2$  to  $(W/L)_1$  be? (4%)

- (b) What is the minimum dc voltage required across current source  $I_1$  for proper operation? If a 0.1-V peak-to-peak signal swing is to be allowed at the drain of  $Q_1$ , what is the highest dc bias voltage that can be used at that node? (4%)

- (c) What is the value of V<sub>SG</sub> of Q<sub>2</sub>, and hence what is the largest value to which V<sub>G2</sub> can be set? (4%)

- (d) What is the minimum dc voltage required across current-source I<sub>2</sub> for proper operation? (4%)

- (e) Given the results of (c) and (d), what is the allowable range of signal swing at the output? (4%)

Fig. 1

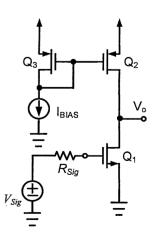

- 2. Consider the integrated-circuit CS amplifier in Fig. 2 for the case  $I_{BIAS}$ =100  $\mu$ A,  $Q_2$  and  $Q_3$  are matched, and  $R_{sig}$ = 200  $k\Omega$ . For  $Q_1$ :  $\mu_n C_{ox}$ =90  $\mu$ A/V²,  $|V_A|$ =12.8 V, W/L=100  $\mu$ m/1.0  $\mu$ m,  $C_{gs}$ =0.2 pF,  $C_{gd}$ =0.015 pF. For  $Q_2$ :  $|V_A|$ =19.2 V. Neglecting the effect of the capacitance inevitably present at the output node. (14%)

- (a) Find the low-frequency gain (5%)

- (b) Find the 3-dB frequency f<sub>H</sub> (5%)

- (c) Find the frequency of the zero f<sub>z</sub> (4%)

Fig. 2

編號: 176、202

# 國立成功大學 109 學年度碩士班招生考試試題

系 所:電機工程學系、電機賞認得院一微電、奈米聯招

考試科目:電子學

考試日期:0210,節次:1

### 第2頁,共3頁

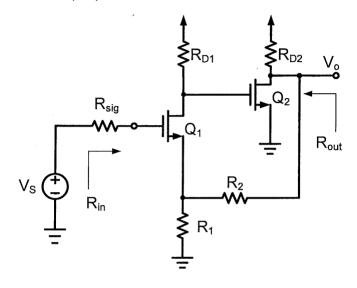

- 3. Fig. 3 shows the feedback circuit with the case  $g_{m1}=g_{m2}=2$  mA/V,  $R_{sig}=200$  k $\Omega$ ,  $R_{D1}=R_{D2}=10$  k $\Omega$ ,  $R_1=1$  k $\Omega$ , and  $R_2=9$  k $\Omega$ . For simplicity, neglect  $r_0$  of each of  $Q_1$  and  $Q_2$ . (16%)

- (a) Find the loop gain  $\beta$ A (4%)

- (b) Find the voltage gain  $V_o/V_s$  (4%)

- (c) Find the input resistance R<sub>in</sub> (4%)

- (d) Find the output resistance Rout. (4%)

Fig. 3

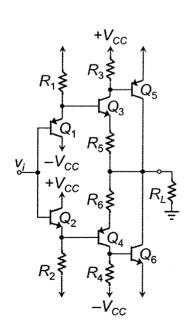

- 4. For the Class AB output stage shown in Fig. 4, we know that  $Q_3$  and  $Q_4$  are the major power BJTs which deliver current to load resistance  $R_L$ . Please give your answer and brief explanation for the following questions: (15%)

- (a) In addition to provide two  $V_{BE}$  voltage drop for biasing the  $Q_3$  and  $Q_4$  like the conventional diode-connected biasing circuit does, what is the major advantage of the input stage which consists of  $Q_1$   $Q_2$ ,  $R_1$  and  $R_2$ ? (5%)

- (b) What is the major purpose of the last stage which consists of  $Q_5$   $Q_6$ ,  $R_3$  and  $R_4$ ? (5%)

- (c) What is the major purpose of the resistors  $R_5$  and  $R_6$ ? (5%)

Fig. 4

編號: 176、>0≥

## 國立成功大學 109 學年度碩士班招生考試試題

系 所:電機工程學系、電機資訊學院一般電、奈米斯特

考試科目:電子學

考試日期:0210,節次:1

### 第3頁,共3頁

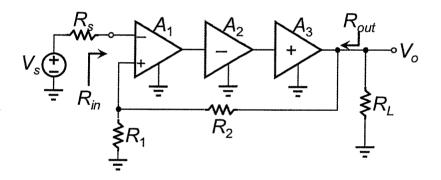

5. Fig. 5 shows a three-stage feedback amplifier: (20%)

$A_1$  has an 82-k $\Omega$  differential input resistance, a 20-V/V open-circuit differential voltage gain, and a 3.2-k $\Omega$  output resistance.

$A_2$  has a 5-k $\Omega$  input resistance, a 20-mA/V short-circuit transconductance, and a 20-k $\Omega$  output resistance.

$A_3$  has an 20-k $\Omega$  input resistance, unity open-circuit voltage gain, and a 1-k $\Omega$  output resistance.

The feedback amplifier feeds a 1-k $\Omega$  load resistance and is fed by a signal source with a 9-k $\Omega$  resistance.

- (a) If  $R_1 = 20 \text{ k}\Omega$ , find the value of  $R_2$  that results in a closed-loop gain  $V_o/V_s$  that is ideally 5V/V. (4%)

- (b) Find the feedback amplifier's input resistance  $R_{in}$ . (4%)

- (c) Find the feedback amplifier's output resistance Rout. (4%)

- (d) If the high-frequency response if the open-loop gain A is dominated by a pole at 100Hz, what is the upper 3-dB frequency of the closed-loop gain? (4%)

- (e) If for some reason,  $A_1$  drops to half its nominal value, what is the percentage change in the closed-loop gain  $A_f$ ? (4%)

Fig. 5

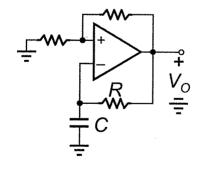

- 6. Please analysis and design an oscillator which uses a bistable circuit. (15%)

- (a) Fig. 6. shows a square waveform generator. The positive and negative saturation levels of the op-amp used in the bistable circuit are  $L_+$  and  $L_-$ , respectively. The trigger levels are  $V_+$  and  $V_-$ . If  $V_\pm = \beta L_\pm$ , derive a relationship between the oscillator period and the time-constant  $\tau = RC$ . (5%)

- (b) Follow 6(a), how to modify the circuit of Fig. 6 to generate a triangular waveform. You are allowed to use one more op amp. (5%)

- (c) Based on the conditions of 6(a), please derive a relationship between the oscillator period and the RC for the circuit you design in 6(b). (5%)

Fig. 6