## 國立高雄師範大學 100 學年度碩士班招生考試試題

(請用藍、黑色筆作答,以其他顏色或鉛筆作答者不予計分)

系所別:電子工程學系

科 目:電子學(第1頁,共2頁)

- 1. (a) Explain the Early Effect in BJT. (5%)

- (b) How to decrease the effect? (5%)

- 2. In Si material, the electron and hole mobility are  $\mu_n$  and  $\mu_p$ , respectively. Which value is the larger? Please explain it. (5%)

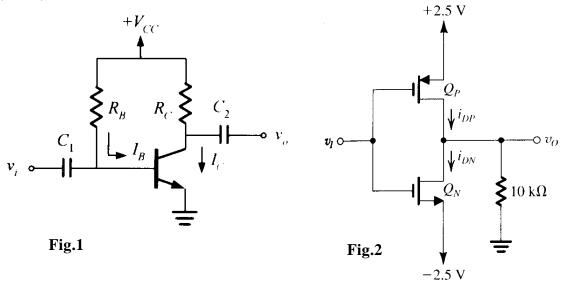

- 3. In Fig.1,  $V_{CC} = 10 \text{ V}$ ,  $R_B = 930 \text{ K}\Omega$ ,  $R_C = 10 \text{ K}\Omega$ ,  $\beta = 150$ , find emitter current  $I_E$ , input impedance  $Z_i$ , current gain  $A_i$ , and voltage gain  $A_V$ . (15%)

- 4. The NMOS and PMOS transistors in Fig.2 are matches with

$k_n'(W_n/L_n) = k_p'(W_p/L_p) = 1mA/V^2$  and  $V_{tn} = -V_{pn} = 1V$ . Assuming  $\lambda = 0$  for the both devices, find the drain currents  $i_{DN}$ ,  $i_{DP}$  and the voltage  $v_0$  for  $v_I = 0$ , +2.5V, and -2.5V. (20%)

- 5. For the MOS differential pair with a common-mode voltage  $v_{CM}$  applied, as shown in Fig.3, let  $V_{DD}=V_{SS}=2$  V,  $k'_n(W/L)=4$  mA/V<sup>2</sup>,  $V_t=0.7$  V, I=0.6 mA, and  $R_D=2.5$  k $\Omega$ , and neglect channel-length modulation.

- (a) Find  $V_{GS}$  for each transistor. (4%)

- (b) For  $v_{CM} = +1$  V, find  $v_s$ ,  $i_{DI}$ , and  $v_{DI}$ . (6%)

- (c) What is the highest value of  $v_{CM}$  for which Q1 and Q2 remain in saturation? (4%)

- (d) If current source I requires a minimum voltage of 0.4 V to operate properly, what is the lowest value allowed for  $v_s$  and hence for  $v_{CM}$ ? (4%)

## (背面有題)

## 系所別:電子工程學系

## 科 目:電子學(第1頁,共2頁)

- 6. Consider the circuit of Fig.4 for the case:  $I=200 \mu A$  and  $V_{OV}=0.25 \text{ V}$ ,  $R_{\text{sig}}=200 \text{ k}\Omega$ ,  $R_D=50 \text{ k}\Omega$ ,  $C_{gs}=C_{gd}=1 \text{ pF}$ .

- (a) Find the dc gain. (4%)

- (b) Find the high-frequency poles. (6%)

- (c) Find an estimate of  $f_H$ . (4%)

- 7. For the circuit of Fig.5, the op amp has open-loop gain  $\mu=10^4$  V/V,  $R_{id}=100$  k $\Omega$ , and  $r_o=1$  k $\Omega$ . Use the feedback method to find:

- (a) The voltage gain  $V_0/V_S$ . (5%)

- (b) The input resistance  $R_{in}$ . (4%)

- (c) The output resistance  $R_{out}$ . (4%)

- 8. Sketch a pseudo-NMOS realization for the function  $Y = \overline{A(B+CD)}$ . (5%)

$\begin{array}{c|c} & & & & \\ \hline = & & \\ \hline R_s=1 \text{ k}\Omega & & \\ \hline V_s & & \\ \hline \end{array}$

Fig.5