## 國立東華大學招生考試試題第一頁,共2

| 招 | 生學  | 年 度 | 101 招 生 類 別 碩士班              |

|---|-----|-----|------------------------------|

| 系 | 所 3 | 班 別 | 電機工程學系 電子工程碩士班、光電工程學系碩士班(乙組) |

| 科 |     | 目   | 電子學                          |

| 注 | 意   | 事項  | 本考科可使用掌上型計算機                 |

- 1. (4%) What are intrinsic and extrinsic semiconductors?

- 2. (10%) (a) Sketch the minority carrier distribution of a uniformly doped  $n^{++}p^{+}n$  BJT operated in the active mode. (b) Explain the base width modulation effect (Early effect) of the BJT.

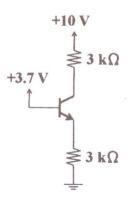

- 3. (6%) For the circuit shown in Fig.1, determine the voltages at all nodes ( $V_B$ ,  $V_C$ , and  $V_E$ ) and the currents in all branches ( $I_B$ ,  $I_C$ , and  $I_E$ ). Assume  $\beta = 100$ , and  $V_{BE} = 0.7$  V.

4. (4%) With the knowledge that  $\mu_p = 0.4 \mu_n$ , what must be the relative width of n-channel and

Fig.1

p-channel devices if they are to have equal drain currents when operated in the saturation mode with overdrive voltages of the same magnitude?

- 5. (6%) Consider an NMOS with  $k_n' = 100 \,\mu\text{A/V}^2$ ,  $V_t = 0.8 \,\text{V}$ , and W/L = 10. Find the drain currents in the following cases.

- (a)  $V_{GS} = 2 \text{ V}$  and  $V_{DS} = 4 \text{ V}$ .

- (b)  $V_{GS} = 4 \text{ V} \text{ and } V_{DS} = 2 \text{ V}.$

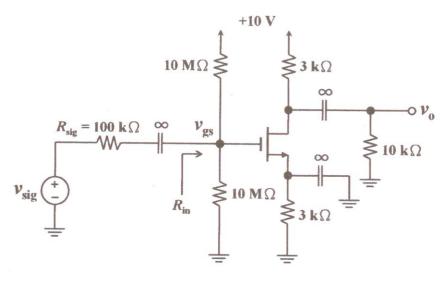

- 6. (20%) Fig.2 shows a CS amplifier. Answer the following questions.

- (a) If the transistor has  $V_t = 1$  V, and  $k_n'(W/L) = 2$  mA/V<sup>2</sup>, find  $V_{GS}$ ,  $I_D$ , and  $V_D$ .

- (b) Find  $g_m$  and  $r_o$  if  $V_A = 100$  V.

- (c) Draw a complete small-signal equivalent circuit.

- (d) Find  $R_{in}$  and  $v_o/v_{sig}$ .

Fig.2

## 國立東華大學招生考試試題第2頁,共2頁

| 招 | 生 | 年 | 度 | 101 招 生 類 別 碩士班              |  |

|---|---|---|---|------------------------------|--|

| 系 | 所 | 班 | 別 | 電機工程學系 電子工程碩士班、光電工程學系碩士班(乙組) |  |

| 科 |   |   | 目 | 電子學                          |  |

| 注 | 意 | 事 | 項 | 本考科可使用掌上型計算機                 |  |

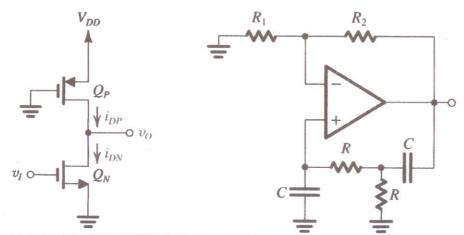

- 7. (15%) Consider a pseudo-NMOS inverter in Fig.3 fabricated in a 0.25 $\mu$ m CMOS technology for which  $\mu_n C_{ox} = 115 \mu A/V^2$ ,  $\mu_p C_{ox} = 30 \mu A/V^2$ ,  $V_{tn} = -V_{tp} = 0.5 V$ , and  $V_{DD} = 2.5 V$ . Let the W/L ratio of  $Q_N$  be (0.375 $\mu$ m/0.25 $\mu$ m) and r=9. Assuming a total capacitance at the inverter output of 7fF, please find:

- (a) NM<sub>H</sub> and NM<sub>L</sub>

- (b)  $t_{PLH}$  and  $t_{PHL}$

- 8. (10%) The Wein-Bridge oscillator is shown in Fig.4.  $R=R_1=10k\Omega$  and C=10nF. Please determine the oscillation frequency and  $R_2$  for oscillation.

- 9. (10%) Design a pseudo-NMOS logic gate circuit which performs the function of  $Y = \overline{A + B + C}$ .

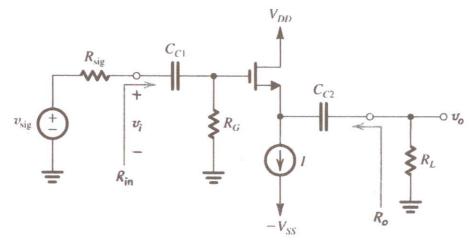

- 10. (15%) Consider a source follower in Fig.5, NMOS transistor is designed with  $g_m=1mA/V$  and  $r_o=150k\Omega$ .  $C_{c1}$  and  $C_{c2}$  are coupling capacitors. Let  $R_{sig}=1M\Omega$ ,  $R_G=4.7M\Omega$  and  $R_L=15k\Omega$ .

- (a) Find  $R_{in}$ ,  $R_o$ , and  $Av = v_o/v_i$ .

- (b) Find the overall small-signal gain  $G_v\!\!=\!\!v_o\!/v_{sig.}$

Fig.5