# 立中正大學101學年度碩士班招生考試試題

Qo = 1; add B Fifth partial product Shift right CAQ

電機工程學系- 信號與媒體通訊組 計算機工程組、晶片系統組 科目:計算機組織

通訊工程學系-網路通訊乙組

第 1頁,共3 頁 第1節

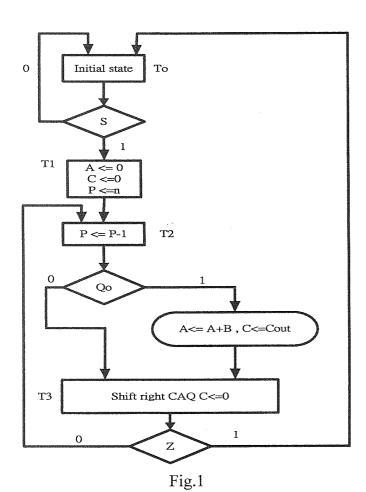

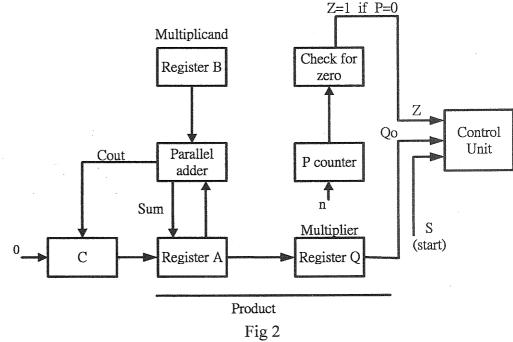

> 1 (12%) Fig.1is the flow chart and Fig.2 is the architectures of binary multiplier. (4%) Give the values of Q. (binary code) 1.2 (8%) Give the second and fifth partial products of CAQ after shift right in Table 1. (binary code)

> > Table 1

#### Multiplicand B = 10110(Carry) (5 bits) (5 bits) P C A Q Multiplier in Q 0 00000 Qo = 1; add B First partial product Shift right CAQ Qo = 1; add B Second partial product Shift right C AQ Qo = 0; shift right CAQ Qo = 0; shift right CAQ

# 立中正大學101學年度碩士班招生考試試題

電機工程學系-信號與媒體通訊組計算機工程組、晶片系統組 科目:計算機組織

通訊工程學系-網路通訊乙組

第1節

第之頁,共了頁

- 2. (10%) Derive the correct floating-point representation for the decimal numbers -13.25 using the 32-bit IEEE 754 floating-point standard and give the largest positive number.

- 3. (9%)Explain the following terms:

- 3.1 Addressing modes

- 3.2 DMA (Direct Memory Access)

- 3.3 Write back vs. Write through

- 4. (9%) A memory data register DR can transfer 32-bit words to M in a single clock cycle. The data items to be stored can be 4, 8, 16, or 32 bits long, and short items are always sign-extended to 32 bits for transmission to M. A 2-bit flag S in the CPU is set to 00, 01, 10, or 11 to indicate a data size of 4, 8, 16, or 32 bits, respectively. Design an efficient logic circuit at the register level to implement the sign extension.

- 5. (10%) Calculate X x Y (X=101011, Y=100011) 5.1 By Robertson multiplication algorithm:

$$x = -2^{n-1} x_{n-1} + \sum_{i=0}^{n-2} 2^{i} x_{i}$$

- 5.2 By Booth's multiplication algorithm.

- 6. (15%) Compare CISC and RISC processors in terms of instruction formats, clock cycle time, clock cycles per instruction, performance, and power consumption. Please explicitly state the reasons of each comparison.

- 7. (25%) Assume that there is no multiplication in the MIPS instruction set. Please implement the function "unsigned int sum(unsigned int n)" which returns

the value of "1 + 2 + ... + n".

- 7.1 Write the C code with a while loop. (5%)

- 7.2 Write the corresponding MIPS code in 7.1. (7%)

- 7.3 Write the C code with recursive procedural calls. (5%)

- 7.4 Write the corresponding MIPS code in 7.3. (8%)

- 8. (10%) Assume an instruction cache miss rate of 2% and a data cache miss rate of 4%. If a machine has a CPI of 2 without any memory stalls and the miss penalty is 40 cycles for all misses, determine how much faster a machine would run with a perfect cache that never missed. Assume 36% of instructions are loads/stores. (Assume that n is mapped to the argument register \$a0.)

# 立中正大學101學年度碩士班招生考試試題

電機工程學系- 信號與媒體通訊組 計算機工程組、晶片系統組 科目:計算機組織

通訊工程學系-網路通訊乙組

第1節

第3頁,共3頁

## MIPS Instruction Set Quick Reference

| Jumps And Branches (Note: One Delay Slot) |               |                                                          |

|-------------------------------------------|---------------|----------------------------------------------------------|

| В                                         | OFF18         | PC += OFF18 <sup>±</sup>                                 |

| BAL                                       | off18         | $R_A = PC + 8$ , $PC += OFF18^{\pm}$                     |

| BEQ                                       | Rs, Rt, off18 | IF Rs = Rt, PC += OFF18*                                 |

| BEQZ                                      | Rs, off18     | IF $R_S = 0$ , $PC += OFF18^{\pm}$                       |

| BGEZ                                      | Rs, off18     | IF Rs $\geq 0$ , PC $+=$ OFF $18^{\pm}$                  |

| BGEZAL                                    | Rs, off18     | $R_A = PC + 8$ ; if $R_S \ge 0$ , $PC += OFF18^{\pm}$    |

| BGTZ                                      | Rs, off18     | IF Rs > 0, PC += OFF $18^{\pm}$                          |

| BLEZ                                      | Rs, off18     | IF Rs $\leq 0$ , PC $+=$ OFF $18^{\pm}$                  |

| BLTZ                                      | Rs, off18     | IF Rs < 0, PC += OFF18 <sup>±</sup>                      |

| BLTZAL                                    | Rs, off18     | $R_A = PC + 8$ ; IF $R_S < 0$ , $PC += OFF18^{\pm}$      |

| BNE                                       | Rs, Rt, off18 | IF Rs $\neq$ Rt, PC += off18 <sup>±</sup>                |

| BNEZ                                      | Rs, off18     | IF Rs $\neq$ 0, PC += OFF18 <sup>±</sup>                 |

| J                                         | ADDR28        | $PC = PC_{31:28} :: ADDR28^{\emptyset}$                  |

| JAL                                       | ADDR28        | $R_A = PC + 8$ ; $PC = PC_{31:28} :: ADDR28^{\emptyset}$ |

| JALR                                      | RD, Rs        | $R_D = PC + 8$ ; $PC = Rs$                               |

| JR                                        | Rs .          | PC = Rs                                                  |

| CONDITION TESTING AND CONDITIONAL MOVE OPERATIONS |                 |                                                          |  |

|---------------------------------------------------|-----------------|----------------------------------------------------------|--|

| MOVN                                              | Rd, Rs, Rt      | IF $RT \neq 0$ , $RD = Rs$                               |  |

| MOVZ                                              | Rd, Rs, Rt      | $_{IF}R_{T}=0, R_{D}=R_{S}$                              |  |

| SLT                                               | Rd, Rs, Rt      | $R_D = (Rs^{\pm} < R_T^{\pm}) ? 1 \div 0$                |  |

| SLTI                                              | Rd, Rs, const16 | $R_D = (Rs^{\pm} < CONST16^{\pm}) ? 1 : 0$               |  |

| SLTIU                                             | RD, Rs, CONST16 | $R_D = (R_S^{\emptyset} < const 16^{\emptyset}) ? 1 : 0$ |  |

| SLTU                                              | Rd, Rs, Rt      | $R_D = (Rs^{\varnothing} < Rr^{\varnothing}) ? 1 : 0$    |  |

### DEFAULT C CALLING CONVENTION (O32)

- Stack Management

The stack grows of The stack grows down.

- Subtract from \$sp to allocate local storage space.

Restore \$sp by adding the same amount at function exit.

- The stack must be 8-byte aligned.

- Modify \$sp only in multiples of eight.

### **Function Parameters**

- Every parameter smaller than 32 bits is promoted to 32 bits.

- First four parameters are passed in registers \$a0-\$a3.

- 64-bit parameters are passed in register pairs:

Little-endian mode: \$a1:\$a0 or \$a3:\$a2.

Big-endian mode: \$a0:\$a1 or \$a2:\$a3.

- Every subsequent parameter is passed through the stack.

- First 16 bytes on the stack are not used.

- Assuming \$sp was not modified at function entry:

- The 1<sup>st</sup> stack parameter is located at 16(\$sp).

The 2<sup>nd</sup> stack parameter is located at 20(\$sp), etc.

- 64-bit parameters are 8-byte aligned.

### Return Values

- 32-bit and smaller values are returned in register \$v0.

- 64-bit values are returned in registers \$v0 and \$v1:

- Little-endian mode: \$v1:\$v0.

- Big-endian mode: \$v0:\$v1.

| REGISTERS |       |                                               |  |  |

|-----------|-------|-----------------------------------------------|--|--|

| 0         | zero  | Always equal to zero                          |  |  |

| 1         | at    | Assembler temporary; used by the assembler    |  |  |

| 2-3       | v0-v1 | Return value from a function call             |  |  |

| 4-7       | a0-a3 | First four parameters for a function call     |  |  |

| 8-15      | t0-t7 | Temporary variables; need not be preserved    |  |  |

| 16-23     | s0-s7 | Function variables; must be preserved         |  |  |

| 24-25     | t8-t9 | Two more temporary variables                  |  |  |

| 26-27     | k0-k1 | Kernel use registers; may change unexpectedly |  |  |

| 28        | gp    | Global pointer                                |  |  |

| 29        | sp    | Stack pointer                                 |  |  |

| 30        | fp/s8 | Stack frame pointer or subroutine variable    |  |  |

| 31        | ra    | Return address of the last subroutine call    |  |  |

| Arithmetic Operations |                 |                                              |  |  |

|-----------------------|-----------------|----------------------------------------------|--|--|

| ADD                   | Rd, Rs, Rt      | $R_D = R_S + R_T$ (overflow trap)            |  |  |

| ADDI                  | Rd, Rs, const16 | $R_D = R_S + const 16^{\pm}$ (overflow trap) |  |  |

| ADDIU                 | Rd, Rs, const16 | $R_D = R_S + const 16^{\pm}$                 |  |  |

| ADDU                  | RD, Rs, RT      | $R_D = R_S + R_T$                            |  |  |

| CLO                   | RD, Rs          | RD = COUNTLEADINGONES(Rs)                    |  |  |

| CLZ                   | RD, Rs          | RD = COUNTLEADINGZEROS(Rs)                   |  |  |

| LA                    | Rd, label       | R <sub>D</sub> = Address(label)              |  |  |

| LI                    | Rd, imm32       | $R_D = IMM32$                                |  |  |

| LUI                   | Rd, const16     | $R_D = const16 << 16$                        |  |  |

| MOVE                  | RD, Rs          | $R_D = R_S$                                  |  |  |

| NEGU                  | RD, Rs          | $R_D = -R_S$                                 |  |  |

| SEB <sup>R2</sup>     | RD, Rs          | $R_{D} = R_{S_{7:0}}^{\pm}$                  |  |  |

| SEH <sup>R2</sup>     | RD, Rs          | $R_D = R_{S_{15:0}}^{\pm}$                   |  |  |

| SUB                   | Rd, Rs, Rt      | $R_D = R_S - R_T$ (OVERFLOW TRAP)            |  |  |

| SUBU                  | Rd, Rs, Rt      | $R_D = R_S - R_T$                            |  |  |

|     | LOAD AND STORE OPERATIONS |                                                                |  |  |

|-----|---------------------------|----------------------------------------------------------------|--|--|

| LB  | RD, OFF16(Rs)             | $R_D = \text{MEM8}(Rs + \text{OFF16}^{\pm})^{\pm}$             |  |  |

| LBU | RD, off16(Rs)             | $R_D = \text{MEM8}(Rs + \text{OFF16}^{\pm})^{\varnothing}$     |  |  |

| LH  | Rd, off16(Rs)             | $R_D = \text{MEM} 16 (Rs + \text{OFF} 16^{\pm})^{\pm}$         |  |  |

| LHU | RD, OFF16(Rs)             | $R_D = \text{MEM} 16 (Rs + \text{OFF} 16^{\pm})^{\varnothing}$ |  |  |

| LW  | RD, OFF16(Rs)             | $R_D = \text{MEM}32(R_S + \text{OFF}16^{\pm})$                 |  |  |

| LWL | Rd, off16(Rs)             | $R_D = LoadWordLeft(Rs + off16^{\pm})$                         |  |  |

| LWR | RD, OFF16(Rs)             | $R_D = L_{OAD}W_{ORD}R_{IGHT}(R_S + off 16^{\pm})$             |  |  |

| SB  | Rs, off16(Rt)             | $MEM8(RT + OFF16^{\pm}) = Rs_{7:0}$                            |  |  |

| SH  | Rs, off16(Rt)             | $MEM16(RT + OFF16^{\pm}) = Rs_{15:0}$                          |  |  |

| sw  | Rs, off16(Rt)             | $MEM32(RT + OFF16^{\pm}) = Rs$                                 |  |  |

| SWL | Rs, off16(Rt)             | StoreWordLeft(Rt + off16 <sup>±</sup> , Rs)                    |  |  |

| SWR | Rs, off16(Rt)             | STOREWORDRIGHT(RT + OFF16 <sup>±</sup> , Rs)                   |  |  |

| ULW | Rd, off16(Rs)             | $R_D = UNALIGNED\_MEM32(Rs + OFF16^{\pm})$                     |  |  |

| USW | Rs, off16(Rt)             | UNALIGNED_MEM $32(R_T + off16^{\pm}) = R_S$                    |  |  |