## 國立臺北大學九十七學年度碩士班招生考試試題

系(所)別:電機工程研究所

組 別:甲組(晶片設計組)

科 目:類比電子學

第 1 頁 共 2 頁 ☑可 □不可使用計算機

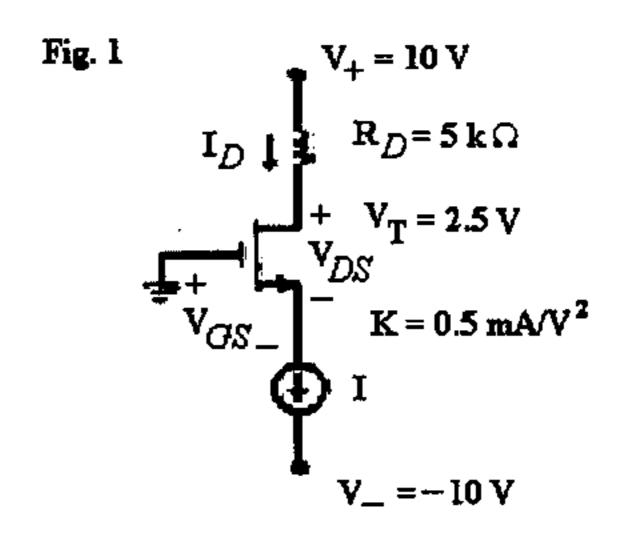

1. For the MOSFET shown in Fig.1 (a) what is the value of I that causes the MOSFET to drop into the ohmic region? (b) with I = 1 mA determine  $V_{GS}$  and  $V_{DS}$  (10%)

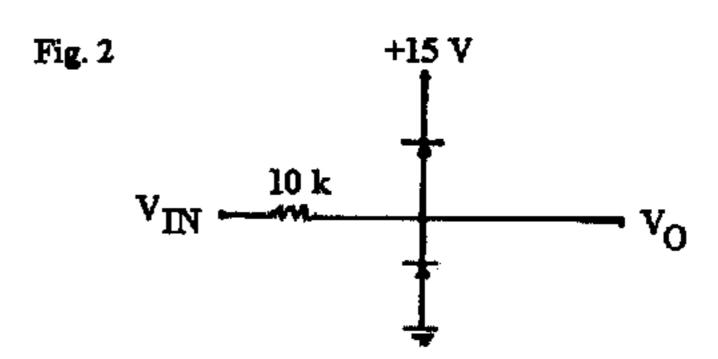

2. In Fig. 2 the diodes have  $V_{D(an)} = 0.7$  volt. Plot and label completely Vo for Vin between -5 and + 25 volts. (10%)

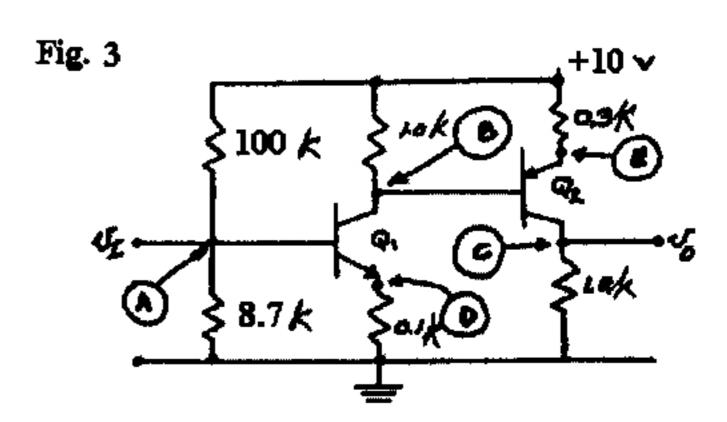

3. In the amplifier shown in Fig. 3, Q1 is npn and Q2 is pnp. Take careful note of the subscripts given here in the following;  $V_{BE1} = V_{EB2} = 0.7$  V. Neglect dc base currents (I<sub>B</sub> is close to zero) and (a) find the dc voltage at nodes A, B, C, D, and E. Fill in the circles above with the correct voltage with respect to ground. (b) What values did you find for the collector currents? (c) Are the transistors Q1 and Q2 active or saturated. (15 %)

- 4. (a) What is channel length modulation effect?

- (b) For a particular n-channel MOS technology, in which the minimum channel length (L) is 1  $\mu$ m, the associated value of  $\lambda$  is 0.01 V<sup>-1</sup>. If a particular device for which L is 3  $\mu$ m operates at Vds = 1 V with a drain current of 80  $\mu$ A, what does the drain current become if Vds is raised to 3 V? What percentage change does this represent? What can be done to reduce the percentage by a factor of 5 ? (10%)

## 國立臺北大學九十七學年度碩士班招生考試試題

系(所)別:電機工程研究所

組 別:甲組(晶片設計組)

科 目:類比電子學

第2頁 共2頁 ☑可 □不可使用計算機

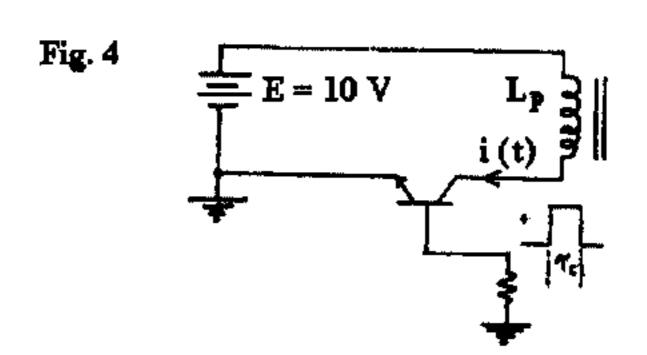

5. The circuit shown in Fig. 4 is the primary of a switched power supply. The transistor is switched into saturation by a periodic pulse train, with each pulse having a during  $\gamma_C$ . The transistor peak current should never exceed 2 amperes under no-load conditions. If  $\gamma_C = 25 \,\mu\text{Sec}$ , find the required value of Lp (inductance). (10%)

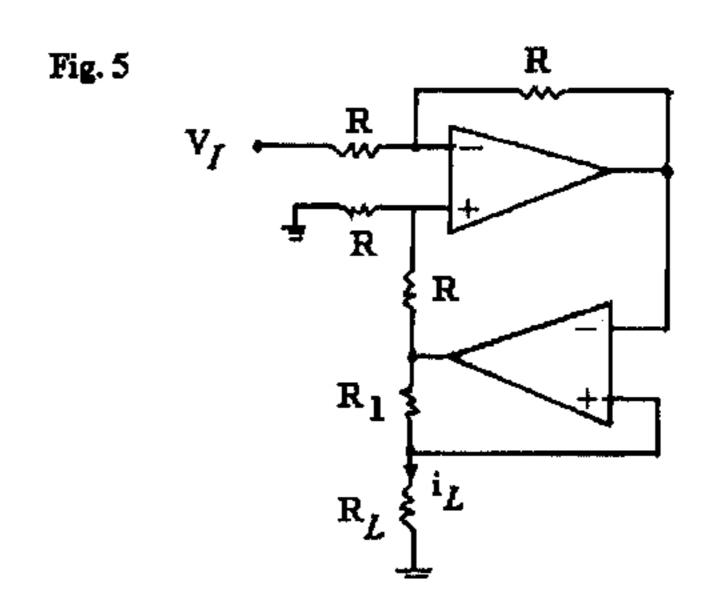

6. Assume ideal op-amps are used in Fig. 5. Calculate i<sub>L</sub> in terms of V<sub>I</sub>. What is the function of this circuit? (15%)

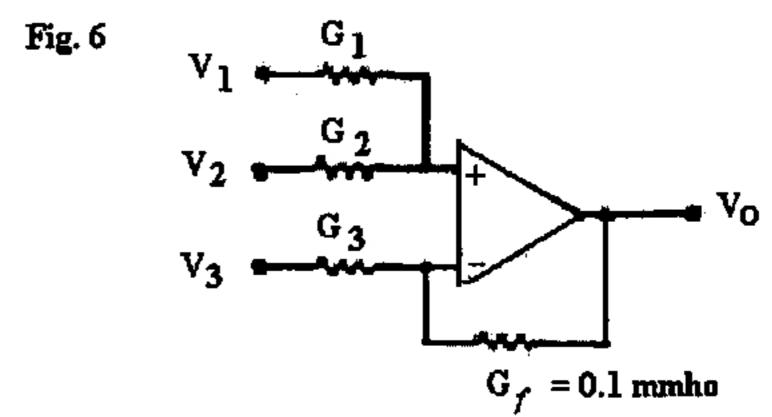

7. Design an OP amp circuit having the form shown in Fig. 6 and give

$$V_0 = V_1 + 4 V_2 - 4 V_3$$

Take  $G_1 + G_2 = G_3 + G_f$  to minimize output offset voltage due to input bias current. Find the values of  $G_1$ ,  $G_2$ , and  $G_3$ . (15%)

8. Using the OP amp-RC circuit to realize a first order high-pass filter with a corner frequency of 10<sup>4</sup> rad/s and a high-frequency gain of 10. Design the values of resistors and capacitor. Also show the circuit. Assume an ideal OP amp is used in this design. (15%)